究竟什么时候开卖呢?

继华擎官网意外自爆后,AMD 旗下首款面向零售的双 CCD 堆叠缓存的处理器 R9-9950X3D2 的足迹出现在了硬件检测工具 CPU-Z 的验证数据库中。这款被玩家认为“真·完全体”的 Zen 5 旗舰,正揭开其神秘面纱的一角。

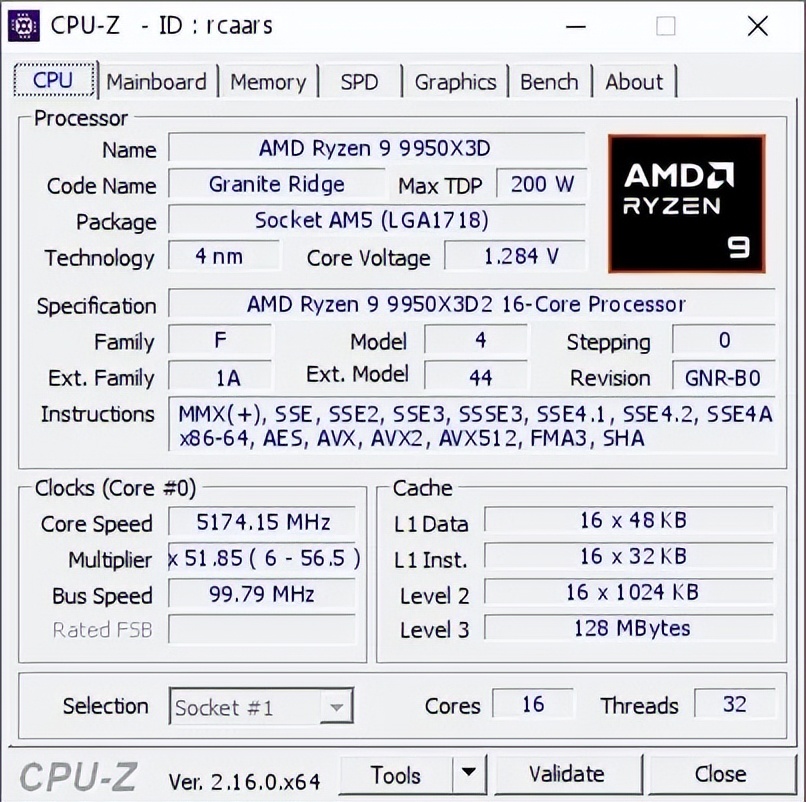

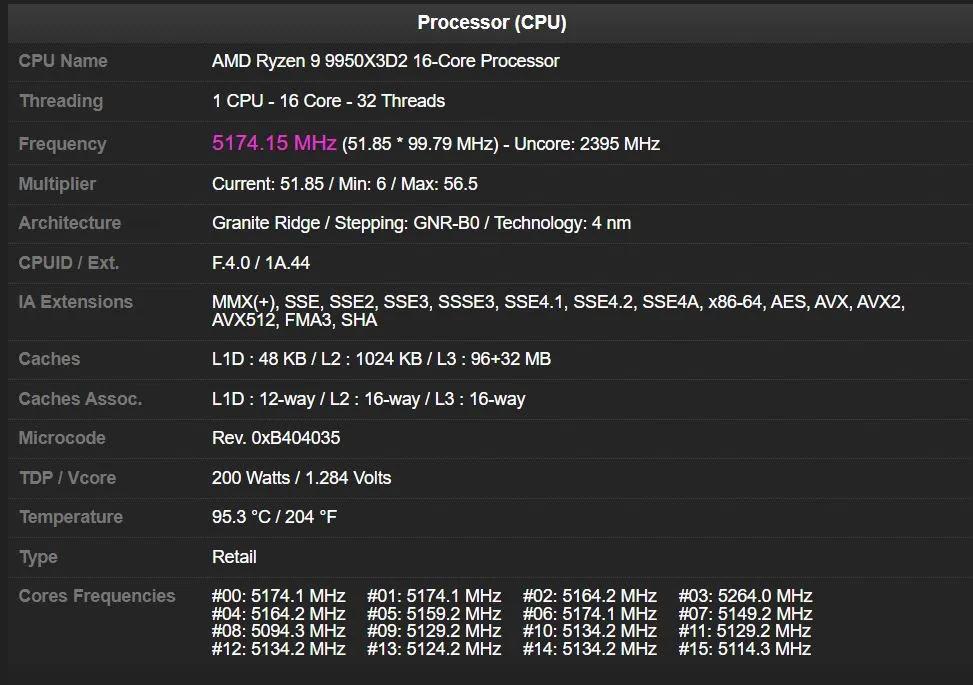

据知名爆料达人 twi@momomo_us 发现,一名匿名用户上传了 9950X3D2 的认证信息。截图显示,该处理器的 TDP 功耗设定从现有的 170W 提升到了惊人的 200W。这意味着 AMD 不再满足于仅仅通过大缓存提升游戏表现,更试图通过更高的功耗上限,解放其在多线程生产力任务中的频率潜能。

不过,此次泄露的缓存规格却引发了不小的争议。CPU-Z 显示该芯片拥有 128MB(96MB+32MB)的三级缓存,这与玩家期待的“192MB 全满血”方案不符。业内分析认为,这并非由于硬件缩水,而是因为当前版本的 CPU-Z 尚未适配这款“双 3D 缓存”架构,导致软件在读取两个 CCD 叠加后的复杂缓存信息时出现了逻辑错误。

在以往的锐龙 9 系列 X3D 处理器中,AMD 通常只在一个 CCD 上堆叠 64MB 的 3D V-Cache,而另一个 CCD 保持原生。这种非对称设计虽然兼顾了游戏与频率,但也给系统调度带来了挑战。而 9950X3D2 的命名后缀“2”明示了其搭载了双份 3D 缓存。若每个 CCD 都拥有 96MB(32MB 原生 + 64MB 堆叠)的 L3 缓存,总容量将达到巨大的 192MB。

随着 DDR5 内存价格在 2026 年的高位震荡,这种通过超大片上缓存来抵消内存延迟的技术路径正变得愈发重要。虽然 AMD 官方尚未正式公布发售时间,但华擎与 CPU-Z 的接连曝光预示着这款“性能怪兽”或许距离正式登场已经不远了。

对于追求极致帧数表现的顶级玩家,以及需要强悍多核性能的内容创作者来说,9950X3D2 的出现或将彻底终结“游戏”与“生产力”不可兼得的局面。当然,前提是你的散热器已经准备好迎接这 200W 的热量释放(算上锐龙积热)。

相关文章